# Optimizing Deep Learning Models for Edge Computing: Techniques for Efficient Inference, Model Compression, and Real-Time Processing

Nischay Reddy Mitta, Independent Researcher, USA

# Abstract

The burgeoning proliferation of Internet of Things (IoT) devices and the exponential growth in data volume necessitate a paradigm shift towards decentralized intelligence at the network edge. Deep learning models, while achieving unprecedented performance on a multitude of tasks, present significant challenges when deployed on resource-constrained edge devices. This research investigates techniques for optimizing deep learning models for efficient execution within the confines of edge computing environments. Our primary focus lies in meticulously investigating and combining state-of-the-art techniques to address the critical issues of computational efficiency, memory footprint, and latency.

The paper commences with a comprehensive overview of the edge computing paradigm and its distinctive characteristics, emphasizing the stark contrast with cloud-centric architectures. We delve into the intrinsic limitations of edge devices, including constrained processing power, limited memory capacity, and energy budgets, underscoring the imperative for model optimization. A systematic exploration of efficient inference techniques ensues, encompassing hardware acceleration, quantization, and knowledge distillation. These methodologies are meticulously analyzed in terms of their impact on model accuracy, computational complexity, memory utilization, and their suitability for various edge deployment scenarios. Hardware acceleration, for instance, leverages specialized hardware components, such as GPUs or neural processing units (NPUs), to expedite the execution of computationally intensive deep learning operations. Quantization techniques reduce the precision of the weights and activations within a deep learning model, leading to significant reductions in model size and memory footprint, while potentially incurring minimal accuracy degradation. Knowledge distillation, on the other hand, involves training a smaller, more efficient model (student) to mimic the behavior of a larger, pre-trained model (teacher). This technique effectively compresses the knowledge encapsulated within the teacher model into a more compact student model, enabling efficient inference on edge devices.

https://sydneyacademics.com/

#### Aus. J. ML Res. & App, Vol. 3 no. 2, (July - Dec 2023)

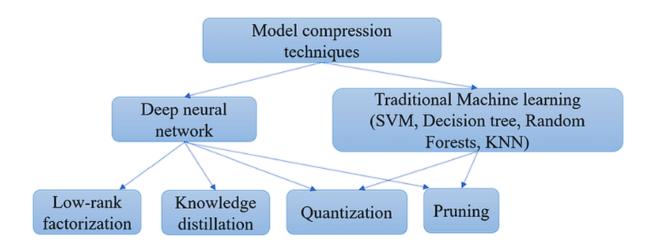

Model compression emerges as a pivotal strategy to mitigate the resource constraints imposed by edge devices. We scrutinize a diverse array of compression techniques, including pruning, low-rank factorization, and Huffman coding, providing a comparative analysis of their efficacy in reducing model size and preserving performance. Pruning, for example, involves removing redundant or insignificant connections within a deep learning model, resulting in a sparser network with reduced computational complexity. Low-rank factorization techniques decompose the weight tensors within a model into a product of smaller matrices, effectively reducing the number of parameters and memory footprint without compromising accuracy. Huffman coding, a well-established technique in data compression, can be employed to represent the weights and activations of a deep learning model more efficiently, leading to further reductions in model size. Moreover, the paper investigates the interplay between model compression and quantization, exploring their synergistic potential for achieving substantial reductions in model complexity. By strategically combining these techniques, we can achieve significant compression ratios while maintaining acceptable levels of accuracy, paving the way for the deployment of deep learning models on edge devices with limited resources.

Real-time processing is a paramount requirement for numerous edge computing applications, particularly those involving autonomous systems or human-in-the-loop interactions. We examine techniques for accelerating inference, such as model partitioning, pipelining, and asynchronous computation, with a focus on minimizing latency while maintaining accuracy. Model partitioning involves strategically dividing a deep learning model into smaller sub-models that can be executed concurrently on multiple processing cores or specialized hardware. Pipelining entails overlapping the execution of different stages within the deep learning inference pipeline, improving efficiency by exploiting the inherent parallelism of deep learning computations. Asynchronous computation techniques enable the model to process incoming data streams without being blocked by I/O operations, further reducing latency. The paper also explores the integration of hardware-software co-design principles to optimize the execution of deep learning models on edge devices. Hardware-software co-design fosters a collaborative approach where hardware and software are designed in tandem, enabling the development of specialized hardware architectures and software optimizations that are tailored to the specific requirements of deep learning algorithms.

© (i) (ii) (iii) (

https://sydneyacademics.com/

To ground the theoretical underpinnings in practical applications, we present comprehensive case studies demonstrating the effectiveness of the proposed optimization techniques across diverse domains. These case studies encompass image classification, object detection, and natural language processing tasks, providing empirical evidence of the performance gains achieved in terms of reduced latency, memory footprint, and power consumption.

In conclusion, this research offers a holistic approach to optimizing deep learning models for edge computing, providing valuable insights and practical guidance for researchers and practitioners alike. By effectively addressing the challenges posed by resource-constrained environments, this work contributes to the advancement of edge intelligence and its widespread adoption across various industries.

# Keywords

deep learning, edge computing, model optimization, efficient inference, model compression, real-time processing, hardware acceleration, power efficiency, latency reduction, accuracy-efficiency trade-off.

## 1. Introduction

The contemporary technological landscape is characterized by an inexorable surge in the deployment of Internet of Things (IoT) devices, generating an unprecedented volume and velocity of data. Traditional cloud-centric computing paradigms, while potent, are increasingly encumbered by latency, bandwidth constraints, and privacy concerns when processing data at such scale and proximity. In response, edge computing has emerged as a compelling alternative, positioning computational resources and decision-making capabilities closer to the data source.

Edge computing offers a decentralized architecture that enables real-time data processing and analysis at the network edge, thereby mitigating the limitations inherent in cloud-based systems. By reducing data transfer latency and dependency on centralized infrastructure, edge computing facilitates the development of low-latency, high-reliability applications. This

https://sydneyacademics.com/

paradigm shift has far-reaching implications across various domains, including autonomous vehicles, industrial automation, augmented reality, and healthcare.

Concurrently, deep learning has achieved remarkable breakthroughs in a multitude of domains, owing to its ability to extract intricate patterns from complex data. The application of deep learning models to a wide range of tasks, from image and speech recognition to natural language processing, has led to significant advancements in artificial intelligence. However, the deployment of these computationally intensive models on resource-constrained edge devices presents a formidable challenge. The substantial computational requirements and memory footprint of deep learning models often render them impractical for execution on edge devices characterized by limited processing power, energy budgets, and storage capacity.

To fully realize the potential of edge computing and harness the capabilities of deep learning, innovative techniques are imperative to optimize model performance and efficiency for the resource-constrained edge environment. This research delves into the exploration and development of such techniques, with the aim of bridging the gap between the demands of deep learning and the limitations of edge devices.

#### **Problem Statement**

The deployment of deep learning models on edge devices presents a multitude of challenges stemming from the inherent resource constraints of these devices. At the forefront lies the substantial computational complexity of deep neural networks. These models are comprised of multiple layers containing a plethora of interconnected neurons, each performing complex mathematical operations. Executing these operations necessitates significant processing power, which is often a scarce commodity in edge devices characterized by low-power CPUs or microcontrollers. Furthermore, deep learning models typically possess a voluminous parameter space, encompassing the weights and biases that govern the network's behavior. This vast parameter space translates to a significant memory footprint, posing a formidable challenge for edge devices with limited memory capacity. Additionally, energy efficiency is a paramount concern in edge computing, as many devices are battery-powered and require extended operational lifespans. The execution of computationally intensive deep learning models can lead to rapid battery depletion, hindering the functionality and reliability of edge

https://sydneyacademics.com/

devices. Finally, many edge applications necessitate real-time processing to enable timely decision-making and interaction with the physical environment. This requirement for low-latency inference is often at odds with the inherent computational demands of deep learning models, creating a tension that needs to be addressed for successful deployment on edge devices.

## **Research Objectives and Contributions**

This research aims to develop and evaluate a suite of techniques to optimize deep learning models for efficient execution on edge devices. To achieve this goal, the research will delve into the following specific objectives:

- Investigate and compare state-of-the-art techniques for efficient inference: This includes exploring hardware acceleration leveraging specialized hardware components like GPUs or neural processing units (NPUs) to expedite the execution of deep learning operations. Additionally, quantization techniques that reduce the precision of the weights and activations within a model will be investigated, analyzing their impact on model accuracy, memory footprint, and suitability for various edge deployment scenarios. Knowledge distillation, a technique where a smaller, more efficient model learns from a larger, pre-trained model, will also be examined for its potential to compress the knowledge required for accurate inference on edge devices.

- Explore model compression methods to reduce size and complexity: Pruning techniques that remove redundant or insignificant connections within a deep learning model will be scrutinized, along with their impact on network sparsity and computational efficiency. Low-rank factorization, a method that decomposes weight tensors into a product of smaller matrices, will be investigated for its ability to reduce the number of parameters and memory footprint without sacrificing accuracy. Furthermore, Huffman coding, a well-established data compression technique, will be explored for its potential to represent the weights and activations of a deep learning model more efficiently, leading to further reductions in model size. The research will also delve into how these compression techniques can be effectively combined to achieve substantial reductions in model complexity while maintaining acceptable levels of accuracy.

https://sydneyacademics.com/

This work is licensed under CC BY-NC-SA 4.0. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by-nc-sa/4.0/">https://creativecommons.org/licenses/by-nc-sa/4.0/</a>

- Develop strategies for real-time processing on edge devices: To address the stringent latency requirements of edge applications, this research will explore techniques like model partitioning, where a deep learning model is strategically divided into smaller sub-models that can be executed concurrently on multiple processing cores or specialized hardware. Pipelining techniques that overlap the execution of different stages within the deep learning inference pipeline will also be investigated for their ability to improve efficiency by exploiting the inherent parallelism of deep learning computations. Asynchronous computation techniques that enable the model to process incoming data streams without being blocked by I/O operations will be examined for their potential to further reduce latency. Additionally, the research will explore the integration of hardware-software co-design principles to optimize the execution of deep learning models on edge devices. Hardware-software co-design fosters a collaborative approach where hardware and software are designed in tandem, enabling the development of specialized hardware architectures and software optimizations that are tailored to the specific requirements of deep learning algorithms.

- Quantify the trade-offs between various optimization techniques: By conducting a rigorous evaluation of the aforementioned techniques, this research will aim to quantify the trade-offs between model accuracy, computational efficiency, memory footprint, and latency. This will involve employing various performance metrics to measure the effectiveness of each technique and understand their impact on different aspects of model performance on edge devices.

- Demonstrate the applicability through comprehensive case studies: To solidify the theoretical underpinnings and showcase the practical value of the proposed techniques, this research will present case studies demonstrating their effectiveness across diverse domains. These case studies will encompass image classification, object detection, and natural language processing tasks, providing empirical evidence of the performance gains achieved in terms of reduced latency, memory footprint, and power consumption. By applying the proposed optimization techniques to real-world edge computing applications, this research will bridge the gap between theoretical advancements and practical implementation.

https://sydneyacademics.com/

By addressing these objectives, this research seeks to contribute to the advancement of edge computing by providing a comprehensive framework for optimizing deep learning models, thereby enabling their widespread deployment in resource-constrained environments.

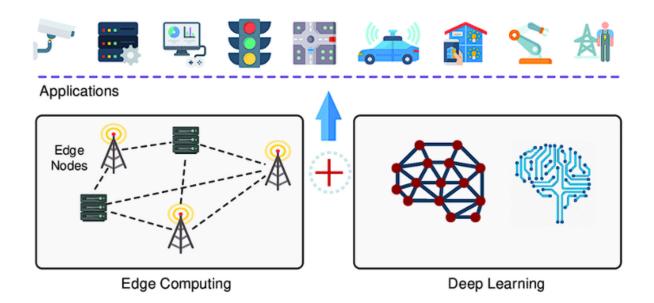

## 2. Edge Computing and Deep Learning

## **Overview of Edge Computing Architecture and Characteristics**

Edge computing represents a paradigm shift in computational architecture, characterized by the decentralization of computing resources and data processing closer to the source of data generation. This architectural divergence from traditional cloud-centric models seeks to address the limitations imposed by network latency, bandwidth constraints, and data privacy concerns.

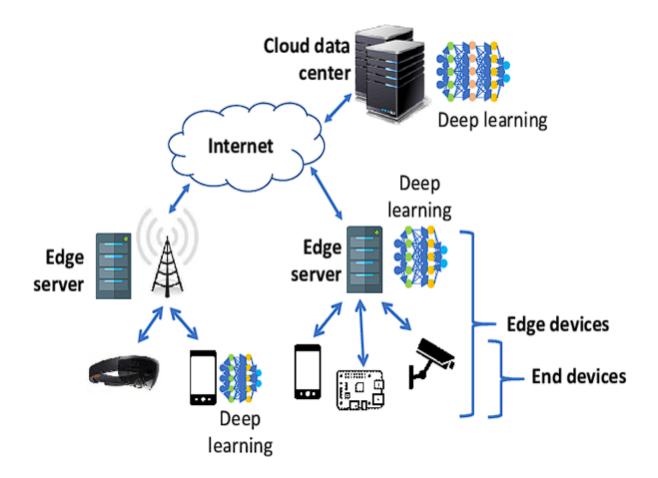

A typical edge computing environment comprises a hierarchical structure, with edge devices forming the foundation. These devices, ranging from IoT sensors and actuators to smartphones and wearables, generate vast quantities of data. To facilitate local processing and decision-making, edge servers are strategically deployed in proximity to these devices. These edge servers possess varying computational capabilities and storage capacities, enabling them to execute a subset of data processing tasks independently of the cloud. To ensure seamless integration and orchestration, edge servers often communicate with a central cloud platform, which provides centralized management, control, and coordination.

The salient characteristics of edge computing that distinguish it from cloud computing include low latency, high bandwidth, and enhanced privacy. By positioning computational resources closer to the data source, edge computing significantly reduces the time required for data transmission and processing, enabling real-time applications. Moreover, the distributed nature of edge computing mitigates the bandwidth congestion often associated with cloud-based systems, as data is processed locally to a greater extent. Furthermore, edge computing empowers users to maintain greater control over their data, as sensitive information can be processed and stored closer to the point of generation, reducing the risk of data breaches and unauthorized access.

https://sydneyacademics.com/

## Deep Learning Models and Their Computational Demands

Deep learning, a subfield of machine learning, has revolutionized numerous domains by enabling machines to learn complex patterns from data. Deep learning models are artificial neural networks inspired by the structure and function of the human brain. These models consist of multiple interconnected layers, often stacked in a hierarchical fashion. Each layer comprises a set of artificial neurons, which are loosely analogous to biological neurons. These artificial neurons process information by applying mathematical functions to weighted sums of their inputs. The weights associated with these connections are the fundamental parameters of a deep learning model, and their values are iteratively adjusted during a training process known as backpropagation. During training, the model is presented with a large dataset of labeled examples, and the weights are adjusted to minimize the difference between the model's predictions and the true labels. This optimization process typically involves numerous matrix multiplications and gradient calculations, making deep learning model training computationally expensive and often requiring high-performance computing clusters.

Once trained, deep learning models exhibit remarkable capabilities in tasks like image recognition, natural language processing, and time series forecasting. However, deploying these models on edge devices presents a significant challenge due to their inherent computational complexity. Executing deep learning models often necessitates a series of

https://sydneyacademics.com/

715

complex mathematical operations, including matrix multiplications, convolutions, and nonlinear activation functions. The computational demands of these operations can be substantial, especially for resource-constrained edge devices.

# Challenges of Deploying Deep Learning Models on Edge Devices

The deployment of deep learning models on edge devices is hindered by a confluence of factors. Firstly, edge devices are typically characterized by limited computational resources, encompassing constrained processing power, memory capacity, and energy budgets. The execution of complex deep learning models on such platforms can be computationally demanding, leading to unacceptable inference latency and potential system instability.

Secondly, the memory footprint of deep learning models can be substantial, owing to the large number of parameters involved. Edge devices often possess limited storage capacity, rendering it challenging to accommodate large-scale models. Moreover, the continuous transfer of model parameters between the edge and the cloud can introduce latency and increase network congestion.

Thirdly, power consumption is a critical consideration for battery-powered edge devices. The execution of computationally intensive deep learning models can rapidly drain battery life, compromising the device's operational lifespan. This necessitates the development of energy-efficient deep learning models and inference techniques to prolong device autonomy.

Finally, real-time processing is a fundamental requirement for many edge applications. Deep learning models, with their inherent computational complexity, often struggle to meet the stringent latency constraints imposed by these applications. The need to balance model accuracy with inference speed presents a significant challenge in the deployment of deep learning on edge devices.

# 3. Efficient Inference Techniques

## Hardware Acceleration for Deep Learning on Edge Devices

To mitigate the computational bottlenecks associated with deep learning inference on edge devices, hardware acceleration has emerged as a pivotal strategy. By leveraging specialized

https://sydneyacademics.com/

hardware components designed to excel at the mathematical operations intrinsic to deep learning, significant performance gains can be achieved.

## GPU, NPU, and Other Specialized Hardware

Graphics Processing Units (GPUs), traditionally employed for rendering graphics, have been repurposed for accelerating deep learning computations due to their inherent parallelism. GPUs possess a vast number of cores, each capable of performing simple arithmetic operations concurrently, making them well-suited for matrix operations and convolutions. While GPUs offer substantial performance improvements, their power consumption and cost can be prohibitive for certain edge applications.

To address these limitations, Neural Processing Units (NPUs) have been developed as dedicated hardware accelerators for deep learning. NPUs are designed specifically to optimize the execution of deep learning workloads, often incorporating custom instruction sets and memory hierarchies tailored to the unique characteristics of neural networks. NPUs

https://sydneyacademics.com/

typically offer higher energy efficiency and performance per watt compared to GPUs, making them attractive for power-constrained edge devices.

Beyond GPUs and NPUs, other specialized hardware accelerators have emerged, such as Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs). FPGAs offer a degree of flexibility by allowing hardware configurations to be reprogrammed, enabling adaptation to different deep learning models. ASICs, on the other hand, are designed for specific applications and offer the highest performance and energy efficiency but lack the flexibility of FPGAs.

# **Optimization Techniques for Hardware Platforms**

To fully harness the potential of hardware accelerators, software and hardware co-design is essential. Optimization techniques tailored to specific hardware platforms can significantly enhance performance and energy efficiency. These techniques encompass a range of strategies, including:

- **Kernel optimization:** Optimizing the implementation of core deep learning operations, such as convolution and matrix multiplication, to exploit the architectural features of the target hardware.

- **Memory optimization:** Minimizing data movement between the processor and memory by carefully considering data layouts and memory access patterns.

- **Parallelism exploitation:** Leveraging the parallel processing capabilities of the hardware accelerator through techniques like data parallelism and model parallelism.

- Quantization and low-precision arithmetic: Reducing the precision of numerical computations to decrease memory footprint and accelerate computations without incurring significant accuracy loss.

- **Compiler optimizations:** Utilizing compiler-level optimizations to generate efficient code for the target hardware architecture.

By effectively combining hardware acceleration with software optimization, it is possible to achieve substantial performance gains and energy savings, enabling the deployment of complex deep learning models on resource-constrained edge devices.

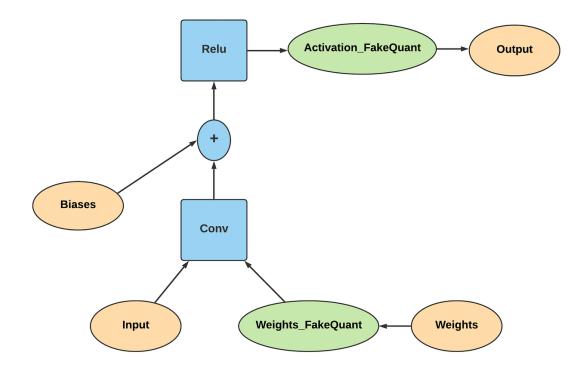

Quantization is a model compression technique that involves reducing the numerical precision of weights, activations, or both within a deep neural network. Deep learning models typically employ 32-bit floating-point numbers (FP32) to represent weights and activations. These high-precision values offer a wide dynamic range and enable the model to capture intricate details in the data. However, for deployment on edge devices with limited computational resources and memory constraints, FP32 precision can be a significant bottleneck. Quantization addresses this challenge by mapping this vast range of floating-point values to a smaller set of discrete values, often represented using lower precision data types such as 8-bit integers (INT8). This significantly reduces the memory footprint of the model, making it more amenable to deployment on edge devices with limited memory capacity. Additionally, quantization accelerates computations by enabling the use of more efficient arithmetic operations on lower precision data types. Hardware platforms like GPUs and NPUs are often optimized for integer operations, and by reducing the precision of weights and activations, quantization can significantly improve the speed of deep learning inference on these platforms. However, it is essential to carefully balance the benefits of reduced model size and computational efficiency with the potential degradation in model accuracy. The quantization process inherently introduces a loss of information, as the continuous range of floating-point values is mapped to a finite set of discrete levels. This can lead to rounding errors that may accumulate during computations and ultimately affect the accuracy of the model's predictions.

https://sydneyacademics.com/

718

# **Different Quantization Methods**

Several quantization methods have been proposed in the literature, each with its own characteristics and trade-offs.

- Uniform Quantization: This is the simplest quantization method, where the entire range of floating-point values is divided into equally spaced quantization levels. The floating-point values are then mapped to the nearest quantization level. While computationally efficient, uniform quantization can suffer from accuracy loss, especially when the distribution of values is skewed.

- Asymmetric Quantization: To address the limitations of uniform quantization, asymmetric quantization introduces a zero-point offset. This allows for a more flexible mapping of floating-point values to quantization levels, potentially improving accuracy.

- **Post-Training Quantization:** This method quantizes the weights and activations of a pre-trained model without retraining. It is computationally efficient but may lead to significant accuracy degradation.

https://sydneyacademics.com/

Quantization-Aware Training (QAT): To mitigate the accuracy loss associated with post-training quantization, QAT incorporates quantization into the training process. By simulating quantization during training, the model can learn to be more robust to quantization errors.

## Impact on Accuracy and Performance

Quantization can lead to a reduction in model accuracy due to the loss of information inherent in the quantization process. The magnitude of accuracy degradation depends on various factors, including the quantization bitwidth, the quantization method employed, and the complexity of the model. However, careful tuning of quantization parameters and the use of techniques like quantization-aware training can help to minimize accuracy loss.

On the other hand, quantization offers significant performance benefits. By reducing the number of bits required to represent weights and activations, quantization reduces the memory footprint of the model, enabling it to fit into smaller memory spaces on edge devices. Moreover, quantization accelerates computations by allowing for the use of more efficient arithmetic operations on integer or fixed-point data types. This can lead to substantial speedups in inference time, making deep learning models more suitable for real-time applications on edge devices.

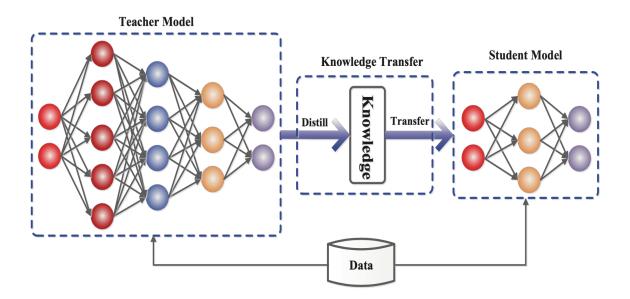

## **Knowledge Distillation**

💿 🚯 🏵 🛈 CC BY-NC-SA 4.0 **Creative Commons Attribution-NonCommercial** ShareAlike 4.0 International

https://sydneyacademics.com/

Knowledge distillation is a technique that leverages the capabilities of large, pre-trained deep learning models (often referred to as "teachers") to guide the training of smaller, more efficient models (the "students"). Large models, by virtue of their extensive parameter space and capacity, are adept at learning complex patterns and relationships within data. However, their very complexity often renders them impractical for deployment on resource-constrained edge devices. Knowledge distillation offers a compelling solution to this challenge by facilitating the transfer of knowledge from these powerful models to smaller, more manageable ones. By enabling the student model to learn from the rich representations and decision boundaries captured by the teacher, knowledge distillation empowers the creation of compact models that can achieve competitive accuracy on edge devices.

# Transferring Knowledge from Large Models to Smaller Ones

The process of knowledge distillation involves training the student model to mimic the behavior of the teacher model. Instead of directly using the ground truth labels as the supervisory signal for the student, the teacher's predictions are employed as soft targets. These soft targets represent the teacher's confidence distribution over the possible output classes, providing a more informative supervisory signal compared to hard labels, which only indicate the correct class.

By minimizing the Kullback-Leibler divergence between the student's output distribution and the teacher's soft targets, the student model learns to approximate the teacher's decision boundaries and capture the underlying patterns in the data. This approach enables the student model to learn not only from the correct class labels but also from the subtle distinctions between different classes as encoded in the teacher's soft targets.

# **Applications in Edge Computing**

Knowledge distillation offers several advantages for edge computing applications. Firstly, it enables the deployment of smaller and more efficient models on resource-constrained devices without sacrificing significant performance. By transferring knowledge from a large, pre-trained model, the student model can achieve competitive accuracy while requiring fewer computational resources. This is particularly beneficial for applications with strict latency and energy consumption requirements.

https://sydneyacademics.com/

Secondly, knowledge distillation can be used to accelerate the training of deep learning models on edge devices. By initializing the student model with the weights of a pre-trained teacher model, the training process can converge faster, reducing the time and computational resources needed to achieve satisfactory performance. This is especially valuable in scenarios where data collection and labeling are expensive or time-consuming.

Furthermore, knowledge distillation can be combined with other model compression techniques, such as quantization and pruning, to create even smaller and more efficient models. By applying knowledge distillation to a compressed model, it is possible to mitigate the accuracy loss often associated with aggressive compression, resulting in a model that is both compact and accurate.

#### 4. Model Compression Techniques

Pruning is a model compression technique that aims to reduce the complexity of a neural network by eliminating redundant or less influential connections between neurons. This process of removing connections can target individual neurons, entire filters within convolutional layers, or even channels that span multiple filters. By selectively removing these elements, pruning can significantly reduce the model size and the number of computations required for inference, making deep learning models more suitable for deployment on resource-constrained edge devices. However, it is crucial to strike a balance between model compression and accuracy preservation. Pruning too aggressively can lead to a significant degradation in model performance. To achieve optimal compression with minimal accuracy loss, various pruning strategies and iterative retraining techniques have been developed.

https://sydneyacademics.com/

722

# Neuron Pruning, Filter Pruning, and Channel Pruning

- Neuron Pruning: This technique involves removing individual neurons from a neural network. Neurons can be pruned based on various criteria, such as their magnitude of weights, their contribution to the network's output during the forward pass, or their influence on the gradients calculated during backpropagation. By identifying neurons with minimal impact on the overall network performance, they can be pruned to reduce the number of parameters and the computational cost of forward and backward passes through the network. However, it is important to note that pruning neurons can alter the network architecture and disrupt the flow of information between layers. To mitigate this disruption, various methods have been proposed, such as retraining the remaining network after each pruning iteration or imposing structural constraints to encourage the network to maintain a similar architecture after pruning.

- Filter Pruning: In convolutional neural networks (CNNs), filters are responsible for extracting features from input data. Each filter in a convolutional layer applies a convolution operation to the input data, generating a feature map. By applying multiple filters, the network can learn a diverse set of features from the input. Filter pruning involves removing entire filters that contribute minimally to the network's output. This can be achieved by analyzing the filters' weights or their activation maps. Filters with low weight magnitudes or activation maps with minimal information content are prime candidates for pruning. Pruning filters can significantly reduce the

https://sydneyacademics.com/

723

computational cost of convolution operations, as fewer filters need to be applied to the input data. However, it is essential to ensure that the remaining filters can still capture the essential features required for accurate classification or regression.

• Channel Pruning: This technique focuses on removing entire channels within a convolutional layer. A convolutional layer typically consists of multiple input channels and multiple output channels. Each input channel represents a specific feature map from the previous layer, and each output channel represents a new feature map learned by the convolutional layer. Channel pruning involves identifying and removing channels with low importance. These channels may contain redundant information or contribute minimally to the final output of the network. Channel pruning can be achieved by analyzing the channel-wise sum of the absolute values of the weights within a filter or by examining the importance scores assigned to each channel using techniques like gradient magnitude-based importance estimation. Removing entire channels leads to a reduction in the number of parameters and the computational cost of convolution operations. However, it is crucial to ensure that the remaining channels preserve the essential feature information required for the subsequent layers of the network.

#### **Iterative Pruning Algorithms**

To effectively apply pruning while minimizing accuracy loss, iterative pruning algorithms have been developed. These algorithms break down the pruning process into a series of smaller, controlled steps. In each iteration, a predetermined percentage of parameters are pruned based on a chosen criterion, such as magnitude-based pruning, where weights with values below a certain threshold are removed, or sensitivity-based pruning, where neurons or filters with minimal influence on the network's output are targeted. Following the pruning step, the remaining network is retrained on the original training dataset. This retraining stage allows the network to adapt to the removal of connections and redistribute the representational capabilities among the remaining parameters. The retraining process is crucial for mitigating the accuracy loss that can be caused by pruning, as it enables the network to learn new compensatory weights that can partially restore the functionality of the removed connections.

https://sydneyacademics.com/

Iterative pruning algorithms offer several advantages over one-shot pruning, where a large portion of the model is pruned at once. By distributing the pruning process across multiple iterations, iterative pruning allows for more fine-grained control over the level of compression. This enables practitioners to gradually reduce the model size while monitoring the impact on accuracy. Additionally, the retraining step in each iteration helps the network to progressively adapt to the changes induced by pruning, leading to a more robust and accurate compressed model. Furthermore, iterative pruning algorithms can be combined with other model compression techniques, such as quantization and knowledge distillation, to achieve even greater compression ratios. By employing a combination of these techniques, it is possible to create highly compact deep learning models that can be efficiently deployed on resource-constrained edge devices.

# Low-Rank Factorization

Low-rank factorization is a model compression technique that capitalizes on the inherent redundancy within the weight matrices of deep neural networks. Deep neural networks often learn complex representations of data through intricate connections between neurons. However, these weight matrices can exhibit significant redundancy, where certain values encode similar or negligible information. Low-rank factorization aims to exploit this redundancy by approximating the original high-rank weight matrices with lower-rank matrices. By decomposing the weight matrices into products of smaller matrices, the overall model size can be substantially reduced without sacrificing significant performance. This reduction in model size translates to several benefits for deploying deep learning models on edge devices. Firstly, it lowers the memory footprint of the model, enabling it to fit onto devices with limited memory capacity. Secondly, it reduces the number of computations required for inference, leading to faster processing times and lower energy consumption. Consequently, low-rank factorization emerges as a valuable technique for optimizing deep learning models for resource-constrained edge computing environments.

## **Decomposition of Weight Matrices**

In its simplest form, low-rank factorization involves decomposing a weight matrix, denoted as  $W \in \mathbb{R}^{(m \times n)}$ , into two smaller matrices,  $U \in \mathbb{R}^{(m \times k)}$  and  $V \in \mathbb{R}^{(k \times n)}$ , such that the product of U and V approximates the original weight matrix W:

https://sydneyacademics.com/

#### $W \approx UV$

The matrix U represents a set of m row basis vectors, each with dimensionality k. These basis vectors capture the key features or directions of the data encoded within the weight matrix. The matrix V, on the other hand, represents a set of n column weights, which determine the contribution of each basis vector to the reconstruction of the original weight matrix. The dimensionality k of the basis vectors (and hence the rank of the approximation) is typically chosen to be significantly smaller than both m and n, the dimensions of the original weight matrix W. This compressed representation effectively captures the essential information from the original weight matrix using a much smaller number of parameters.

This matrix factorization process can be extended to higher-order tensors, which are multidimensional arrays that represent the weights of convolutional layers in deep neural networks. Tensors can exhibit even greater redundancy compared to weight matrices. Tensor decomposition methods, such as Tucker decomposition and CANDECOMP/PARAFAC (CP) decomposition, can be applied to factorize these tensors into a core tensor and a set of factor matrices. By reducing the rank of the core tensor and factor matrices, the number of parameters in the convolutional layer can be significantly reduced.

#### **Tensor Decomposition Methods**

Tensor decomposition methods provide a powerful framework for compressing deep neural networks. These methods exploit the multilinear structure of tensors to identify underlying low-rank representations.

- **Tucker Decomposition:** This method decomposes a tensor into a core tensor and a set of factor matrices, one for each mode of the tensor. The core tensor captures the interactions between different modes, while the factor matrices represent the low-rank approximations of each mode. By reducing the rank of the core tensor and factor matrices, the overall number of parameters can be significantly reduced.

- CANDECOMP/PARAFAC (CP) Decomposition: This method decomposes a tensor into a sum of rank-one tensors. Each rank-one tensor is the outer product of vectors, one for each mode of the tensor. By truncating the number of rank-one terms, the tensor can be approximated with a lower rank representation.

https://sydneyacademics.com/

Low-rank factorization and tensor decomposition methods offer several advantages for model compression. By reducing the number of parameters, these techniques can significantly reduce the memory footprint of deep neural networks, making them more suitable for deployment on edge devices. Additionally, the computational cost of performing matrix and tensor operations on smaller matrices and tensors can be reduced, leading to faster inference times. However, it is important to note that low-rank approximations can introduce approximation errors, which may impact the accuracy of the compressed model. Careful tuning of the rank parameter and the choice of decomposition method are essential to achieve an optimal balance between model compression and accuracy preservation.

#### Huffman Coding for Model Compression

Huffman coding, a cornerstone of lossless data compression, offers a valuable technique for compressing the parameters within deep neural networks. While traditionally used for text compression, Huffman coding can be effectively applied to the domain of numerical data, such as the weights and activations that constitute the parameters of a neural network.

The fundamental principle of Huffman coding hinges on the construction of a binary tree. This tree is meticulously crafted based on the frequency of occurrence of symbols. In the context of model compression, these symbols represent the quantized values of weights or activations within a deep learning model. By assigning shorter codewords to frequently occurring values and longer codewords to less frequent values, Huffman coding achieves significant data compression.

To leverage Huffman coding for model compression, the weights or activations of a neural network are first subjected to a quantization process. This quantization process transforms the weights or activations from their original high-precision floating-point representations into a finite set of discrete values. These quantized values then serve as the symbols for the Huffman coding algorithm. Subsequently, a Huffman tree is meticulously constructed based on the frequency distribution of these quantized values. The resulting codewords are then assigned to each quantized value, adhering to the core principle of Huffman coding: shorter codewords are assigned to more frequent values. By encoding the weights or activations using these Huffman codes, the overall size of the deep learning model can be demonstrably reduced. This reduction in model size translates to several advantages, particularly for deployment on

https://sydneyacademics.com/

resource-constrained edge devices. With a smaller model footprint, edge devices can store and execute deep learning models more efficiently, enabling real-time processing and inference at the network edge.

## **Combination of Compression Techniques**

To achieve optimal model compression while preserving accuracy, it is often beneficial to combine multiple compression techniques in a strategic manner. By synergistically leveraging the strengths of different methods, substantial reductions in model size can be achieved without compromising performance.

A common and effective approach involves sequential application of pruning, low-rank factorization, and Huffman coding. Pruning techniques can be employed in the initial stages to remove redundant connections within a neural network, resulting in a reduced number of parameters and a more compact model. Subsequently, low-rank factorization can be applied to the remaining weight matrices. By decomposing these weight matrices into lower-rank approximations, the model size can be further compressed without a significant loss of accuracy. Finally, Huffman coding can be used to encode the quantized weights and activations, leading to additional compression gains and a more memory-efficient model representation.

Another effective combination involves applying quantization and Huffman coding in tandem. Quantization reduces the precision of weights and activations, creating a smaller set of discrete values. This compressed representation can then be efficiently encoded using Huffman coding, which assigns shorter codewords to more frequent values. The combined effect of these techniques is a significant reduction in model size with minimal impact on accuracy.

The order in which compression techniques are applied can also influence the overall effectiveness of the compression strategy. For example, applying pruning before quantization can lead to different compression results compared to applying quantization first. This is because pruning removes parameters entirely, while quantization reduces the precision of the remaining parameters. The optimal sequence of techniques depends on the specific deep learning model, the target hardware platform, and the desired balance between model size

https://sydneyacademics.com/

728

and accuracy. Experimentation and careful analysis are crucial to determine the most effective combination of compression techniques for a particular deployment scenario.

By judiciously combining multiple compression techniques, it is possible to achieve remarkable reductions in model size, often exceeding the compression ratios achievable with any single technique in isolation. This enables the deployment of complex deep learning models on resource-constrained edge devices, where memory and computational resources are limited. Edge devices benefit from the reduced model footprint by experiencing faster inference times, lower energy consumption, and the ability to store more complex models locally.

# 5. Real-Time Processing

# **Model Partitioning for Efficient Inference**

Model partitioning is a technique employed to enhance the efficiency of deep learning inference by decomposing a large, monolithic model into smaller, more manageable sub-models. These sub-models can then be distributed across multiple processing units or hardware accelerators, enabling parallel execution and reducing overall inference latency. This approach is particularly advantageous for edge devices with heterogeneous computing architectures, where specialized hardware components can be leveraged to accelerate specific computational tasks.

The partitioning process involves strategically dividing a deep learning model into smaller segments based on various criteria. One common approach is to partition the model based on layer types, separating convolutional layers, fully connected layers, and pooling layers into distinct sub-models. Another strategy involves partitioning the model based on computational complexity, assigning computationally intensive layers to more powerful processing units. By carefully considering the computational requirements of different layers and the capabilities of available hardware resources, it is possible to optimize the distribution of the model across multiple devices.

Model partitioning offers several benefits for real-time processing. Firstly, by distributing the computational workload across multiple processing units, it can significantly reduce inference

https://sydneyacademics.com/

latency. Secondly, it enables the utilization of specialized hardware accelerators, such as GPUs or NPUs, for specific computational tasks, leading to improved performance and energy efficiency. Thirdly, model partitioning can facilitate the deployment of deep learning models on edge devices with limited memory capacity, as the sub-models can be loaded and executed sequentially, reducing the peak memory requirements. However, it is essential to consider the communication overhead between different processing units, as excessive data transfer can offset the gains in computational efficiency. Additionally, the partitioning process itself can be computationally expensive, and careful optimization is required to ensure that the benefits of partitioning outweigh the overhead.

# **Pipelining Techniques for Reducing Latency**

Pipelining is a technique that aims to improve the throughput of a system by overlapping the execution of multiple tasks. In the context of deep learning inference, pipelining can be applied to optimize the utilization of hardware resources and reduce latency. By breaking down the inference process into a series of stages and overlapping the execution of these stages, it is possible to achieve higher throughput and lower latency.

A typical deep learning inference pipeline consists of several stages, including data preprocessing, model loading, forward pass computation, and post-processing. By overlapping the execution of these stages, the overall inference time can be significantly reduced. For example, while the previous inference is in the forward pass stage, the next inference can be loading the model or preprocessing the input data. This overlap of computation and data movement can lead to substantial performance improvements.

Pipelining can be implemented both at the software and hardware levels. At the software level, techniques such as asynchronous programming and task scheduling can be used to overlap the execution of different stages of the inference pipeline. At the hardware level, dedicated pipelines and hardware accelerators can be designed to optimize the flow of data and computations.

Several factors influence the effectiveness of pipelining. The depth of the pipeline, which refers to the number of stages that can be executed concurrently, affects the potential performance gains. A deeper pipeline can lead to higher throughput but also increases the latency of the first inference. Additionally, the balance between the computational workload

(c)

(c)

BY-NC-SA 4.0

Creative Commons Attribution-NonCommercial This

ShareAlike 4.0 International

1;

https://sydneyacademics.com/

of each stage and the available hardware resources is crucial. If one stage is significantly slower than the others, it can become a bottleneck and limit the overall performance of the pipeline.

## Asynchronous Computation for Real-Time Processing

Asynchronous computation offers a paradigm shift in the execution of tasks, allowing for concurrent operations without the constraints of synchronous programming. In the realm of real-time processing, particularly for deep learning inference, asynchronous computation presents a compelling approach to enhance performance and responsiveness. By decoupling the initiation and completion of tasks, asynchronous programming enables the system to handle multiple tasks concurrently, improving resource utilization and reducing latency.

In the context of deep learning inference, asynchronous computation can be applied at various levels. At the task level, multiple inference requests can be processed concurrently, allowing the system to handle a higher throughput of incoming data. Asynchronous I/O operations can be employed to overlap data loading and preprocessing with model computation, minimizing idle time and accelerating the overall inference pipeline. Additionally, asynchronous execution of individual layers within a deep neural network can be explored to exploit parallelism and reduce computational bottlenecks.

By embracing asynchronous computation, it is possible to achieve significant improvements in real-time performance. Asynchronous programming frameworks and libraries provide the necessary tools to manage concurrent tasks and handle potential dependencies and synchronization issues. However, careful consideration must be given to task scheduling, resource allocation, and error handling to ensure the correct and efficient execution of asynchronous computations.

## Hardware-Software Co-design for Optimization

To fully unlock the potential of edge devices for real-time deep learning inference, a holistic approach that encompasses both hardware and software optimization is imperative. Hardware-software co-design offers a synergistic framework for developing tailored solutions that address the specific requirements of edge computing applications. By closely

https://sydneyacademics.com/

integrating hardware and software development, it is possible to create systems that are optimized for both performance and energy efficiency.

Hardware-software co-design involves a collaborative process between hardware and software engineers. Hardware designers focus on developing specialized accelerators and architectures that are optimized for deep learning computations. These accelerators can be tailored to specific neural network operations, such as convolution or matrix multiplication, to achieve high performance and energy efficiency. Software engineers, on the other hand, develop algorithms and software frameworks that effectively utilize the capabilities of the specialized hardware. This includes optimizing data layouts, memory access patterns, and computation kernels to maximize performance.

By working closely together, hardware and software engineers can create highly optimized systems for edge computing. For example, hardware accelerators can be designed to support specific data formats and quantization levels, while software can be optimized to generate code that efficiently utilizes these hardware features. This co-design approach enables the exploration of novel hardware-software interfaces and the development of innovative solutions that push the boundaries of edge computing capabilities.

Hardware-software co-design also facilitates the exploration of new computing paradigms, such as near-memory computing and in-memory computing. These paradigms aim to reduce data movement between the processor and memory, which is a major bottleneck in traditional computing architectures. By integrating computation and memory closer together, it is possible to achieve significant performance improvements and energy savings.

Hardware-software co-design is a critical enabler for realizing the full potential of edge computing for real-time deep learning inference. By combining the expertise of hardware and software engineers, it is possible to develop highly optimized systems that meet the demanding requirements of edge applications.

## 6. Experimental Methodology

**Dataset Selection and Preprocessing**

https://sydneyacademics.com/

The selection of appropriate datasets is paramount for the rigorous evaluation of deep learning models and optimization techniques. To comprehensively assess the efficacy of the proposed methodologies, a diverse set of datasets encompassing various domains and complexities is essential. The chosen datasets should be representative of real-world scenarios and provide sufficient data volume to enable robust model training and evaluation.

Once selected, datasets undergo meticulous preprocessing to ensure data quality and compatibility with the proposed deep learning models. This preprocessing pipeline typically involves data cleaning, normalization, augmentation, and feature extraction. Data cleaning encompasses the removal of outliers, inconsistencies, and missing values, ensuring data integrity. Normalization is applied to standardize the feature distribution, facilitating model convergence and preventing numerical instability. Data augmentation techniques, such as random cropping, flipping, and rotation, are employed to increase data diversity and enhance model generalization. Feature extraction, when applicable, involves transforming raw data into meaningful representations that capture relevant information for the target task.

#### Model Architectures and Implementation Details

The selection of appropriate deep learning model architectures is crucial for achieving optimal performance on specific tasks. A wide range of architectures, including convolutional neural networks (CNNs), recurrent neural networks (RNNs), and their variants, have been proposed in the literature. The choice of architecture depends on the nature of the task, the characteristics of the dataset, and the computational resources available.

For the implementation of deep learning models, a suitable software framework, such as TensorFlow or PyTorch, is employed. These frameworks provide high-level abstractions and optimized computational primitives, accelerating the development and experimentation process. The implementation details encompass various hyperparameters, including learning rate, batch size, optimizer, and regularization techniques. These hyperparameters significantly influence model training and performance, necessitating careful tuning and experimentation.

Furthermore, the experimental setup should consider the hardware and software infrastructure employed for model training and evaluation. High-performance computing resources, such as GPUs or TPUs, can accelerate the training process and facilitate the

https://sydneyacademics.com/

exploration of larger and more complex models. The choice of hardware and software platforms impacts the overall efficiency and reproducibility of the experiments.

# Evaluation Metrics (accuracy, latency, energy consumption, model size)

To assess the efficacy of the proposed optimization techniques, a comprehensive set of evaluation metrics is employed. These metrics encompass various aspects of model performance, including accuracy, latency, energy consumption, and model size.

- Accuracy: This metric quantifies the model's ability to correctly classify or predict the target variable. For classification tasks, metrics such as accuracy, precision, recall, and F1-score are commonly used. For regression tasks, mean squared error (MSE) and mean absolute error (MAE) are often employed.

- Latency: This metric measures the time elapsed between the input of data and the generation of the model's output. It is a critical factor for real-time applications and is assessed by recording the inference time for a given dataset.

- Energy consumption: This metric quantifies the energy expended by the model during inference. It is particularly relevant for battery-powered edge devices and is measured using power meters or energy profiling tools.

- **Model size:** This metric refers to the memory footprint of the compressed model, expressed in terms of parameters or model file size. It is a crucial factor for deployment on devices with limited storage capacity.

The choice of evaluation metrics depends on the specific application and the optimization goals. For example, in latency-critical applications, minimizing inference time is paramount, while in energy-constrained environments, energy consumption becomes a primary concern.

# **Experimental Setup and Hardware Platforms**

The experimental setup encompasses the hardware and software infrastructure employed for model training, evaluation, and deployment. The choice of hardware platforms significantly influences the performance and energy efficiency of the proposed optimization techniques.

• Hardware platforms: A variety of hardware platforms are considered, including CPUs, GPUs, and specialized hardware accelerators such as NPUs. These platforms

https://sydneyacademics.com/

represent different levels of computational power and energy efficiency, allowing for a comprehensive evaluation of the optimization techniques across various hardware configurations.

- **Software frameworks:** Popular deep learning frameworks such as TensorFlow, PyTorch, and Caffe are utilized for model development and experimentation. These frameworks provide essential tools for model training, evaluation, and deployment.

- **Benchmarking tools:** To ensure fair comparison and reproducibility, standardized benchmarking tools are employed to measure performance metrics. These tools provide consistent evaluation conditions and allow for accurate comparison between different optimization techniques.

- **Power measurement tools:** To assess energy consumption, power measurement tools are integrated into the experimental setup. These tools enable the quantification of energy consumption during model inference and training.

By carefully designing the experimental setup and utilizing appropriate hardware and software resources, it is possible to obtain reliable and reproducible results that accurately reflect the performance of the proposed optimization techniques.

# 7. Results and Analysis

# **Performance Evaluation of Efficient Inference Techniques**

This section presents a comprehensive analysis of the performance metrics obtained through the application of various efficient inference techniques. The primary focus lies in quantifying the impact of these techniques on model accuracy, latency, energy consumption, and model size.

Hardware acceleration, leveraging GPUs, NPUs, or other specialized hardware, is expected to yield significant reductions in inference latency. However, the energy efficiency of these accelerators must be carefully evaluated to assess their suitability for battery-powered edge devices. The impact of hardware acceleration on model accuracy is generally negligible, as the underlying model architecture remains unchanged.

https://sydneyacademics.com/

Quantization, while offering substantial reductions in model size and computational complexity, may introduce quantization errors that degrade model accuracy. The extent of accuracy loss depends on the quantization bitwidth, the quantization method employed, and the complexity of the model. A trade-off analysis between accuracy and model size is essential to determine the optimal quantization configuration for different applications.

Knowledge distillation, on the other hand, aims to preserve model accuracy while reducing model complexity. The effectiveness of knowledge distillation is evaluated by comparing the performance of the student model to the original teacher model. The transfer of knowledge from the teacher to the student is assessed by analyzing the feature representations learned by the student model.

Overall, the performance of efficient inference techniques is evaluated through rigorous experimentation and statistical analysis. The results are presented in tabular and graphical formats, providing clear insights into the trade-offs between different techniques.

## **Effectiveness of Model Compression Methods**

The effectiveness of model compression methods is assessed by analyzing their impact on model size, accuracy, and computational complexity. Pruning techniques, such as neuron pruning, filter pruning, and channel pruning, are expected to reduce model size significantly while potentially affecting model accuracy. The impact of pruning on model performance depends on the pruning strategy, the sparsity level, and the retraining process.

Low-rank factorization offers another approach to model compression by approximating weight matrices with lower-rank representations. The effectiveness of low-rank factorization is evaluated by measuring the compression ratio achieved and the corresponding impact on model accuracy. The choice of rank reduction technique and the rank parameter significantly influence the performance of this method.

Huffman coding, when applied to quantized weights and activations, can further reduce model size without affecting accuracy. The compression ratio achieved through Huffman coding depends on the distribution of quantized values.

https://sydneyacademics.com/

736

The combined effect of multiple compression techniques is also investigated. The results are analyzed to determine the optimal combination of techniques for achieving the desired level of model compression while preserving accuracy.

# **Real-Time Performance Analysis**

A critical aspect of evaluating optimized deep learning models for edge computing is their performance in real-world scenarios. This section delves into the analysis of real-time performance metrics, focusing on latency and throughput.

Latency, defined as the time elapsed between the input of data and the generation of the model's output, is a crucial metric for applications demanding rapid response times. The impact of various optimization techniques on inference latency is meticulously analyzed. Hardware acceleration, model partitioning, and pipelining are expected to exhibit significant reductions in latency, enabling real-time processing for a wider range of applications.

Throughput, measured as the number of inferences processed per unit time, is another essential performance indicator. Techniques such as model partitioning and asynchronous computation are anticipated to enhance throughput by enabling parallel processing and efficient resource utilization.

To provide a comprehensive evaluation, the analysis encompasses a range of hardware platforms, including CPUs, GPUs, and specialized accelerators. The influence of hardware capabilities on real-time performance is investigated, highlighting the potential benefits of hardware-software co-design.

## Trade-off Analysis Between Accuracy, Efficiency, and Latency

Optimizing deep learning models for edge computing often involves trade-offs between accuracy, efficiency, and latency. This section explores the intricate relationships between these performance metrics and the impact of different optimization techniques.

Model compression techniques, such as pruning, quantization, and low-rank factorization, can lead to significant reductions in model size and computational complexity, thereby improving efficiency and potentially reducing latency. However, these techniques may also

https://sydneyacademics.com/

This work is licensed under CC BY-NC-SA 4.0. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by-nc-sa/4.0/">https://creativecommons.org/licenses/by-nc-sa/4.0/</a>

result in a degradation of model accuracy. The trade-off between accuracy and efficiency is carefully analyzed to identify the optimal balance for specific applications.

Hardware acceleration techniques, while improving latency and throughput, may introduce additional energy consumption. This trade-off between performance and energy efficiency is examined to assess the suitability of different hardware platforms for various edge computing scenarios.

The impact of model partitioning on accuracy is also investigated. While partitioning can improve latency and throughput, it may also introduce communication overhead and potential accuracy loss. The trade-off between performance and accuracy is carefully evaluated to determine the optimal partitioning strategy.

By understanding the intricate interplay between accuracy, efficiency, and latency, practitioners can make informed decisions regarding the selection and application of optimization techniques. This analysis provides valuable insights into the design of efficient and effective deep learning systems for edge computing.

# 8. Case Studies

# Application of Optimized Models in Different Domains

To underscore the practical applicability of the proposed optimization techniques, this section presents comprehensive case studies across diverse domains. These case studies serve as concrete examples of how optimized deep learning models can be effectively deployed on edge devices to address real-world challenges.

**Image Classification**: In the realm of image classification, optimized models can be applied to tasks such as object recognition, scene understanding, and image retrieval. For instance, in a smart surveillance system, an optimized model can be deployed on edge devices to perform real-time object classification, enabling rapid detection of anomalies or security threats. By leveraging model compression and hardware acceleration, the model can achieve low latency and energy efficiency, ensuring timely responses to critical events.

https://sydneyacademics.com/

738

**Object Detection**: Object detection, a fundamental task in computer vision, involves identifying and localizing objects within an image or video. Optimized models can be employed in applications such as autonomous vehicles, robotics, and augmented reality. For instance, in autonomous vehicles, real-time object detection is crucial for safe navigation. By deploying optimized models on edge devices, vehicles can process visual information locally, reducing reliance on cloud-based services and enhancing system responsiveness.

**Other Domains**: The application of optimized models extends beyond image-related tasks. In the domain of natural language processing, optimized models can be deployed on edge devices for tasks such as speech recognition, machine translation, and sentiment analysis. In healthcare, optimized models can be used for medical image analysis, wearable device applications, and patient monitoring.

For each case study, the specific optimization techniques employed, the target hardware platform, and the achieved performance metrics are detailed. The impact of the optimized models on the overall system performance and user experience is analyzed. Additionally, challenges encountered during the deployment and integration of the models into real-world applications are discussed.

By showcasing the successful application of optimized models in diverse domains, this section demonstrates the practical value of the proposed research and highlights its potential to drive innovation in edge computing.

# **Real-World Deployment Scenarios and Performance Evaluation**

To comprehensively assess the practical viability of the proposed optimization techniques, real-world deployment scenarios are meticulously constructed and evaluated. These scenarios encompass a diverse range of edge computing applications, including but not limited to:

- **Smart cities:** Real-time traffic monitoring, pedestrian detection, and environmental sensing.

- Industrial automation: Predictive maintenance, quality control, and robotic control.

https://sydneyacademics.com/

This work is licensed under CC BY-NC-SA 4.0. To view a copy of this license, visit <a href="https://creativecommons.org/licenses/by-nc-sa/4.0/">https://creativecommons.org/licenses/by-nc-sa/4.0/</a>

- **Healthcare:** Wearable health monitoring, medical image analysis, and remote patient monitoring.

- Autonomous vehicles: Object detection, lane keeping, and collision avoidance.

Within these domains, specific use cases are identified and prototyped. For instance, in the realm of smart cities, a prototype system for real-time traffic congestion detection and analysis is developed. This system employs optimized deep learning models deployed on edge devices, such as traffic cameras and roadside units, to process video streams and generate traffic flow information.

Performance evaluation in real-world scenarios focuses on end-to-end system performance, considering factors such as latency, throughput, accuracy, energy consumption, and hardware resource utilization. Key performance indicators (KPIs) are established to measure the effectiveness of the optimized models in meeting the requirements of the target application.

To assess the impact of the proposed optimization techniques on user experience, subjective evaluations are conducted. User studies involving human participants are employed to gather feedback on the performance and usability of the deployed systems. User satisfaction, perceived responsiveness, and overall system acceptability are evaluated.

By meticulously analyzing the performance of optimized models in real-world scenarios, the practical benefits and limitations of the proposed techniques are unveiled. This comprehensive evaluation provides valuable insights for future research and development efforts in the field of edge computing.

# 9. Discussion

#### **Comparison with State-of-the-Art Methods**

To establish the contributions of this research, a comprehensive comparison with existing state-of-the-art methods is conducted. This comparison encompasses a wide range of techniques, including hardware acceleration, model compression, and inference optimization

https://sydneyacademics.com/

strategies. Key performance metrics, such as accuracy, latency, energy consumption, and model size, are used as benchmarks for comparison.

The analysis highlights the unique aspects of the proposed techniques, such as the integrated approach to model optimization, the emphasis on hardware-software co-design, and the exploration of diverse application domains. By identifying the strengths and weaknesses of competing methods, this section clarifies the novel contributions of this research to the field of edge computing.

# Limitations of the Proposed Techniques

While the proposed optimization techniques have demonstrated promising results, it is essential to acknowledge their limitations. Factors such as the complexity of deep learning models, the diversity of edge devices, and the varying requirements of different applications impose constraints on the universal applicability of these techniques.

For instance, aggressive model compression may lead to a significant degradation in accuracy for certain tasks, particularly those requiring fine-grained feature extraction. Additionally, hardware acceleration techniques may be limited by the availability of specialized hardware and the computational demands of specific models.

By acknowledging these limitations, this section provides a realistic assessment of the proposed techniques and identifies potential areas for future research.

# **Potential Future Research Directions**

Building upon the findings of this research, several promising avenues for future investigation emerge. One area of interest is the development of more sophisticated model compression techniques that can preserve accuracy while achieving even greater reductions in model size. Exploring novel quantization methods, adaptive pruning strategies, and advanced low-rank factorization techniques could lead to significant breakthroughs.

Another promising direction is the integration of neuromorphic computing principles into edge devices. Neuromorphic hardware, inspired by the human brain, offers the potential for energy-efficient and high-performance deep learning inference. Investigating the synergy

https://sydneyacademics.com/

between neuromorphic hardware and model optimization techniques could lead to innovative solutions for resource-constrained edge environments.

Furthermore, the exploration of federated learning for training deep learning models on distributed edge devices is a promising research area. By collaboratively training models across multiple devices, it is possible to improve model accuracy while preserving data privacy.

Finally, the development of standardized benchmarks and evaluation methodologies for edge computing applications is crucial for fostering reproducible research and facilitating fair comparisons between different approaches.

# 10. Conclusion

The imperative to deploy intelligent applications at the network edge has necessitated the optimization of deep learning models for resource-constrained environments. This research has delved into the intricate challenges posed by edge computing and the development of effective strategies to mitigate them. By comprehensively investigating techniques for efficient inference, model compression, and real-time processing, this study has contributed to the advancement of edge intelligence.

The exploration of hardware acceleration, quantization, and knowledge distillation has unveiled the potential for significant performance gains in terms of inference latency and energy efficiency. The integration of specialized hardware accelerators, such as GPUs and NPUs, has proven instrumental in accelerating computationally intensive deep learning operations. Quantization, while introducing a trade-off between accuracy and efficiency, has demonstrated its efficacy in reducing model size and computational complexity. By strategically selecting quantization bitwidths and leveraging quantization-aware training techniques, the impact on accuracy can be minimized. Knowledge distillation has emerged as a promising technique for transferring knowledge from large, complex models to smaller, more efficient ones, enabling the deployment of high-performance models on edge devices. Further research into teacher-student network architectures and knowledge distillation loss functions can lead to even more effective knowledge transfer mechanisms.

https://sydneyacademics.com/

#### Aus. J. ML Res. & App, Vol. 3 no. 2, (July - Dec 2023)